# Design and Analysis of Robust Low Voltage Static Random Access Memories

by

Daeyeon Kim

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2012

Doctoral Committee:

Professor Dennis Michael Sylvester, Chair Professor David Blaauw Professor Trevor N. Mudge Assistant Professor Kenn Richard Oldham C Daeyeon Kim 2012

All Rights Reserved

To my family

#### ACKNOWLEDGEMENTS

During my graduate study, I have been supported by many people both inside and outside of the University of Michigan. I would like begin by expressing my gratitude to my advisor, Professor Dennis Sylvester, for his tremendous support and guidance. He has been a great mentor throughout my Ph.D. by showing directions in my works, encouraging me when I was down, and sharing me his passion as a scholar, as an innovator, and as an advisor. I would also like to thank Professor David Blaauw for practically being a co-advisor. He always has been enthusiastic and supportive in discussing and sharing new ideas and implementing them. I would like to thank Professor Trevor Mudge and Professor Kenn Oldham for being a member of my dissertation committee members and helping review my dissertation.

Inside the university, I have worked with many intelligent and smart people. My special appreciation goes to Jae-sun Seo and Mingoo Seok. They have helped me in countless ways since I started my graduate study, even after they graduated from the university. Gregory Chen and Michael Wieckowski helped me to learn fundamental ideas related to SRAM design and tape-outs. Matthew Fojtik worked in designing CPU and preparing testing environments in Chapter III. Sudhir Satpathy and Bharan Giridhar helped me in developing ideas and designing circuits in Chapter IV. Yoonmyung Lee and I worked together in analyzing a new device in Chapter V. David Fick and Nathaniel Pinckney worked as student administrators of a server pool (vlsipool) for simulations and tape-outs. I also enjoyed having discussions with members in our research group: Mohammad Hassan Ghaed, Dongsuk Jeon, Yen-Po Chen, Suyoung Bang, Prashant Singh, Nurrachman Liu, Zhi Yoong Foo, Gyouho Kim, Yejoong Kim, Inhee Lee, and Dongmin Yoon. Besides work, I would also like to thank all my friends in Ann Arbor for having a wonderful time and sharing memories.

I also have been supported from outside the university. During internships in the industry, co-works with many talented mentors deepened and extended my knowledge on state-of-the-art SRAM design. I would like to appreciate Dr. Robert Aitken, Dr. Vikas Chandra, and Mr. Cezary Pietrzyk at ARM, Inc. for mentoring me. I would also like to thank the Korea Foundation for Advanced Studies for funding my fellowship.

Last but not the least, I am grateful to my family for their love and support. I would like to express special gratitude to my wife, Mi Yon Kim, for her love, support, and patience during my graduate study.

# TABLE OF CONTENTS

| DEDICATIO   | N                                                            | ii   |

|-------------|--------------------------------------------------------------|------|

| ACKNOWLE    | DGEMENTS                                                     | iii  |

| LIST OF FIG | URES                                                         | viii |

| LIST OF TAI | BLES                                                         | xii  |

| LIST OF AB  | BREVIATIONS                                                  | xiii |

| ABSTRACT    |                                                              | XV   |

| CHAPTER     |                                                              |      |

| I. Intro    | $\operatorname{duction}$                                     | 1    |

| 1.1         | Technology Scaling and Low Power Design                      | 2    |

| 1.2         | Challenges of Designing Low Voltage SRAM                     | 4    |

| 1.3         | Contributions of This Work                                   | 6    |

| II. Writa   | ability Analysis for Bit-Interleaved 8-T SRAMs               | 10   |

| 2.1         | Introduction                                                 | 11   |

| 2.2         | Background and Related Works                                 | 13   |

|             | 2.2.1 Write Failure and Read Disturb                         | 13   |

|             | 2.2.2 Static Noise Margin Analysis                           | 15   |

|             | 2.2.3 Soft Error and Half Select Disturb                     | 19   |

|             | 2.2.4 Writability vs. Half Select Disturb in Bit-Interleaved |      |

|             | 8-T SRAMs                                                    | 20   |

| 2.3         | Writability Analysis Method                                  | 21   |

|             | 2.3.1 SRAM Dynamic Writability Metric                        | 21   |

|             | 2.3.2 SRAM Worst Case Corner Simulation                      | 22   |

|             | 2.3.3 Bit-Interleaved Writability Analysis                   | 26   |

| 2.4         | Writability Analysis at Near-Threshold                       | 27   |

|             | 2.4.1 Word-line Boosting                                     | 27   |

| III. Design of Low Leakage SRAM333.1Introduction333.2Background and Related Works353.2.1Leakage Mechanisms353.2.2Leakage Reduction Techniques373.2.3Technology Selection for Leakage Reduction443.3Design of Low Leakage SRAM443.3.1SRAM Bitcell and Operation Modes443.3.2Bit-line Boosting for Fast Write Operation463.3.3Body Biasing with Boosted Supply473.3.4Leakage Reduction during Standby Mode483.3.5Read Buffer Design513.4Measurement Results523.5Conclusion56IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs584.1Introduction594.2Background and Related Works604.2.3&-T SRAM Operations at Low Voltage604.2.3&-T SRAM Write Time624.2.4&-T SRAM Static Failures and Half Select Disturb664.3Design of Adaptive Write Architecture694.3.1Write Word-Line Pulse Width Modulation704.4Measurement Results724.4.1Prototype Implementation724.4.2Measurement Data744.5Conclusion80V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors815.1Introduction825.2Background and Related Works845.2.1Nece                                                                                                                                                                                                                 |            | 2.4.2 Device Sizing Optimization                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------|

| III. Design of Low Leakage SRAM333.1Introduction333.2Background and Related Works353.2.1Leakage Mechanisms353.2.2Leakage Reduction Techniques373.2.3Technology Selection for Leakage Reduction443.3Design of Low Leakage SRAM443.3.1SRAM Bitcell and Operation Modes443.3.2Bit-line Boosting for Fast Write Operation463.3.3Body Biasing with Boosted Supply473.3.4Leakage Reduction during Standby Mode483.3.5Read Buffer Design513.4Measurement Results523.5Conclusion56IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs584.1Introduction594.2Background and Related Works604.2.1Variation at Low Voltage604.2.28-T SRAM Operations at Low Voltage604.2.38-T SRAM Write Time624.2.48-T SRAM Static Failures and Half Select Disturb664.3Design of Adaptive Write Architecture694.3.1Write Word-Line Pulse Width Modulation704.4.2Measurement Results724.4.1Prototype Implementation724.4.2Measurement Data744.5Conclusion80V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors815.1Introduction825.2Backgr                                                                                                                                                                                                                 |            | 2.4.3 Dual Writability Enhancement                   |

| 3.1       Introduction       33         3.2       Background and Related Works       35         3.2.1       Leakage Mechanisms       35         3.2.2       Leakage Reduction Techniques       37         3.2.3       Technology Selection for Leakage Reduction       44         3.3       Design of Low Leakage SRAM       44         3.3.1       SRAM Bitcell and Operation Modes       44         3.3.2       Bit-line Boosting for Fast Write Operation       46         3.3.3       Body Biasing with Boosted Supply       47         3.3.4       Leakage Reduction during Standby Mode       48         3.3.5       Read Buffer Design       51         3.4       Leakage Reduction during Standby Mode       48         3.3.5       Conclusion       52         3.5       Conclusion       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Write Time       62         4.2.3       8-T SRAM Write Failures and H                                                                             | 2.5        | Conclusion                                           |

| 3.2Background and Related Works353.2.1Leakage Mechanisms353.2.2Leakage Reduction Techniques373.2.3Technology Selection for Leakage Reduction443.3Design of Low Leakage SRAM443.3.1SRAM Bitcell and Operation Modes443.3.2Bit-line Boosting for Fast Write Operation463.3.3Body Biasing with Boosted Supply473.3.4Leakage Reduction during Standby Mode483.3.5Read Buffer Design513.4Measurement Results523.5Conclusion56IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs4.1Introduction594.2Background and Related Works604.2.1Variation at Low Voltage604.2.28-T SRAM Operations at Low Voltage604.2.38-T SRAM Operations at Low Voltage664.2.48-T SRAM Static Failures and Half Select Disturb664.2.5Previous Works664.3Design of Adaptive Write Architecture694.3.1Write Word-Line Voltage Level Modulation724.4.1Prototype Implementation724.4.2Measurement Data744.5Conclusion80V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors815.1Introduction825.2Background and Related Works845.2.1Necessity for Steep Subthreshold Sw                                                                                                                                                                                         | III. Desig | n of Low Leakage SRAM                                |

| 3.2.1Leakage Mechanisms $35$ $3.2.2$ Leakage Reduction Techniques $37$ $3.2.3$ Technology Selection for Leakage Reduction $44$ $3.3$ Design of Low Leakage SRAM $44$ $3.3.1$ SRAM Bitcell and Operation Modes $44$ $3.3.2$ Bit-line Boosting for Fast Write Operation $46$ $3.3.3$ Body Biasing with Boosted Supply $47$ $3.3.4$ Leakage Reduction during Standby Mode $48$ $3.3.5$ Read Buffer Design $51$ $3.4$ Measurement Results $52$ $3.5$ Conclusion $56$ IV. Adaptive Write Architecture for Low Voltage 8-T SRAMS $58$ $4.1$ Introduction $59$ $4.2$ Background and Related Works $60$ $4.2.1$ Variation at Low Voltage $60$ $4.2.2$ $8$ -T SRAM Operations at Low Voltage $60$ $4.2.3$ $8$ -T SRAM Operations at Low Voltage $66$ $4.2.3$ $8$ -T SRAM Write Time $62$ $4.2.4$ $8$ -T SRAM Static Failures and Half Select Disturb $66$ $4.3.1$ Write Word-Line Pulse Width Modulation $69$ $4.3.1$ Write Word-Line Pulse Width Modulation $70$ $4.4$ Measurement Results $72$ $4.4.2$ Measurement Data $74$ $4.5$ Conclusion $80$ V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors $81$ $5.1$ Introduction $82$ $5.2$ Background and Related Works $84$ $5.2.1$ <                                                        | 3.1        | Introduction                                         |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.2        | Background and Related Works                         |

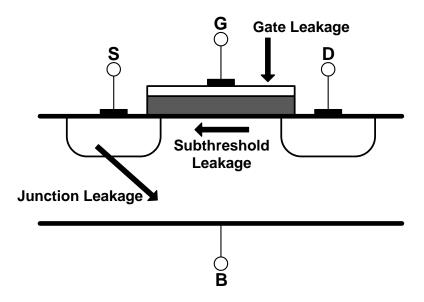

| 3.2.3       Technology Selection for Leakage Reduction       44         3.3       Design of Low Leakage SRAM       44         3.3.1       SRAM Bitcell and Operation Modes       44         3.3.1       SRAM Bitcell and Operation Modes       44         3.3.2       Bit-line Boosting for Fast Write Operation       46         3.3.3       Body Biasing with Boosted Supply       47         3.3.4       Leakage Reduction during Standby Mode       48         3.3.5       Read Buffer Design       51         3.4       Measurement Results       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.5       Previous Works       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Voltage Level Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       72         4.4.1       Prototype Implementation       72 <td></td> <td>3.2.1 Leakage Mechanisms</td> |            | 3.2.1 Leakage Mechanisms                             |

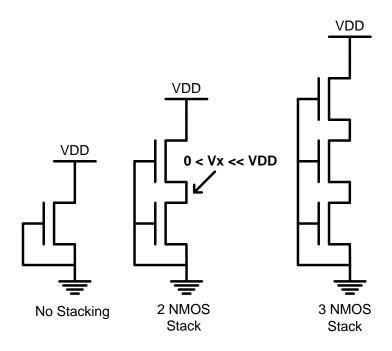

| 3.3       Design of Low Leakage SRAM       44         3.3.1       SRAM Bitcell and Operation Modes       44         3.3.2       Bit-line Boosting for Fast Write Operation       46         3.3.3       Body Biasing with Boosted Supply       47         3.3.4       Leakage Reduction during Standby Mode       48         3.3.5       Read Buffer Design       51         3.4       Measurement Results       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs         58       4.1       Introduction         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Write Time       62         4.2.4       8-T SRAM Static Failures and Half Select Disturb       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Results       72         4.4.1       Prototype Implementation       72                                                            |            | 3.2.2 Leakage Reduction Techniques                   |

| 3.3.1       SRAM Bitcell and Operation Modes       44         3.3.2       Bit-line Boosting for Fast Write Operation       46         3.3.3       Body Biasing with Boosted Supply       47         3.3.4       Leakage Reduction during Standby Mode       48         3.3.5       Read Buffer Design       51         3.4       Leakage Reduction during Standby Mode       48         3.3.5       Read Buffer Design       51         3.4       Measurement Results       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Static Failures and Half Select Disturb       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Voltage Level Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data                                                 |            | 3.2.3 Technology Selection for Leakage Reduction 4   |

| 3.3.2       Bit-line Boosting for Fast Write Operation       46         3.3.3       Body Biasing with Boosted Supply       47         3.3.4       Leakage Reduction during Standby Mode       48         3.3.5       Read Buffer Design       51         3.4       Measurement Results       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Write Time       62         4.2.4       8-T SRAM Static Failures and Half Select Disturb       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors       81                                                              | 3.3        | Design of Low Leakage SRAM                           |

| 3.3.3       Body Biasing with Boosted Supply       47         3.3.4       Leakage Reduction during Standby Mode       48         3.3.5       Read Buffer Design       51         3.4       Measurement Results       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Write Time       62         4.2.4       8-T SRAM Write Tailures and Half Select Disturb       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors       81         5.1       Introduction       82         5.2<                                                           |            | 3.3.1 SRAM Bitcell and Operation Modes               |

| 3.3.4       Leakage Reduction during Standby Mode       48         3.3.5       Read Buffer Design       51         3.4       Measurement Results       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Write Time       62         4.2.4       8-T SRAM Write Time       62         4.2.5       Previous Works       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-       81         5.1       Introduction       82         5.2       Background and Related Works       8                                                                             |            | 3.3.2 Bit-line Boosting for Fast Write Operation 4   |

| 3.3.5       Read Buffer Design       51         3.4       Measurement Results       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Operations at Low Voltage       60         4.2.4       8-T SRAM Write Time       62         4.2.5       Previous Works       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subth                                                                    |            | 3.3.3 Body Biasing with Boosted Supply               |

| 3.4       Measurement Results       52         3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Operations at Low Voltage       60         4.2.4       8-T SRAM Write Time       62         4.2.4       8-T SRAM Static Failures and Half Select Disturb       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1                                                                   |            | 3.3.4 Leakage Reduction during Standby Mode 4        |

| 3.5       Conclusion       56         IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Operations at Low Voltage       60         4.2.4       8-T SRAM Write Time       62         4.2.4       8-T SRAM Static Failures and Half Select Disturb       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                          |            | 3.3.5 Read Buffer Design                             |

| IV. Adaptive Write Architecture for Low Voltage 8-T SRAMs       58         4.1 Introduction       59         4.2 Background and Related Works       60         4.2.1 Variation at Low Voltage       60         4.2.2 8-T SRAM Operations at Low Voltage       60         4.2.3 8-T SRAM Operations at Low Voltage       60         4.2.4 8-T SRAM Write Time       62         4.2.5 Previous Works       66         4.3 Design of Adaptive Write Architecture       69         4.3.1 Write Word-Line Pulse Width Modulation       69         4.3.2 Write Word-Line Voltage Level Modulation       70         4.4 Measurement Results       72         4.4.1 Prototype Implementation       72         4.4.2 Measurement Data       74         4.5 Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors       81         5.1 Introduction       82         5.2 Background and Related Works       84         5.2.1 Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                          | 3.4        | Measurement Results                                  |

| 4.1       Introduction       59         4.2       Background and Related Works       60         4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Write Time       62         4.2.4       8-T SRAM Write Time       62         4.2.5       Previous Works       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-         ing Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                    | 3.5        | Conclusion                                           |

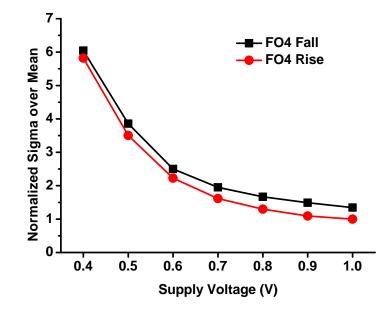

| 4.2.1       Variation at Low Voltage       60         4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Write Time       62         4.2.4       8-T SRAM Static Failures and Half Select Disturb       66         4.2.5       Previous Works       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                 |            |                                                      |

| 4.2.2       8-T SRAM Operations at Low Voltage       60         4.2.3       8-T SRAM Write Time       62         4.2.4       8-T SRAM Static Failures and Half Select Disturb       66         4.2.5       Previous Works       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-<br>ing Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                  | 4.2        | 0                                                    |

| 4.2.3       8-T SRAM Write Time       62         4.2.4       8-T SRAM Static Failures and Half Select Disturb       66         4.2.5       Previous Works       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                                                      |

| 4.2.4       8-T SRAM Static Failures and Half Select Disturb .       66         4.2.5       Previous Works .       66         4.3       Design of Adaptive Write Architecture .       69         4.3.1       Write Word-Line Pulse Width Modulation .       69         4.3.2       Write Word-Line Pulse Width Modulation .       69         4.3.2       Write Word-Line Voltage Level Modulation .       70         4.4       Measurement Results .       72         4.4.1       Prototype Implementation .       72         4.4.2       Measurement Data .       74         4.5       Conclusion .       80         V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors .         5.1       Introduction .       81         5.2       Background and Related Works .       84         5.2.1       Necessity for Steep Subthreshold Swing .       84                                                                                                                                                                                                                                                                                                                                                                                 |            | 1 0                                                  |

| 4.2.5       Previous Works       66         4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-<br>ing Transistors         5.1       Introduction       81         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                                                      |

| 4.3       Design of Adaptive Write Architecture       69         4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-<br>ing Transistors         5.1       Introduction       81         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                                      |

| 4.3.1       Write Word-Line Pulse Width Modulation       69         4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-<br>ing Transistors         5.1       Introduction       81         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43         |                                                      |

| 4.3.2       Write Word-Line Voltage Level Modulation       70         4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-<br>ing Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.0        |                                                      |

| 4.4       Measurement Results       72         4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-<br>ing Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                                                      |

| 4.4.1       Prototype Implementation       72         4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-<br>ing Transistors         5.1       Introduction       81         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4        | č                                                    |

| 4.4.2       Measurement Data       74         4.5       Conclusion       80         V. Low Power Circuit Design Based on Heterojunction Tunnel-<br>ing Transistors         5.1       Introduction       81         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                                      |

| V. Low Power Circuit Design Based on Heterojunction Tunneling Transistors       81         5.1 Introduction       82         5.2 Background and Related Works       84         5.2.1 Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | *                                                    |

| ing Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5        | Conclusion                                           |

| ing Transistors       81         5.1       Introduction       82         5.2       Background and Related Works       84         5.2.1       Necessity for Steep Subthreshold Swing       84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V Low      | Power Circuit Design Based on Heterojunction Tunnel- |

| 5.2 Background and Related Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                                                      |

| 5.2 Background and Related Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5.1        | Introduction                                         |

| 5.2.1 Necessity for Steep Subthreshold Swing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.2        | 8                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                                                      |

| 5.3 HETT Device Physics and Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.3        | - °                                                  |

|           | 5.3.1    | HETT Device Physics                | 86  |

|-----------|----------|------------------------------------|-----|

|           |          | HETT Device Modeling               | 88  |

| 5.4       | HETT-I   | Based Circuit Analysis             | 90  |

|           | 5.4.1    | Dynamic Power Reduction            | 90  |

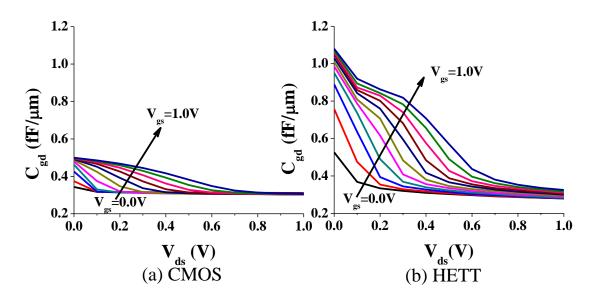

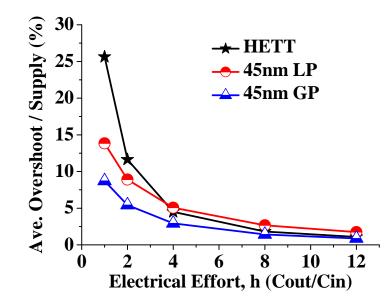

|           | 5.4.2    | Limitations of HETT-Based Circuits | 92  |

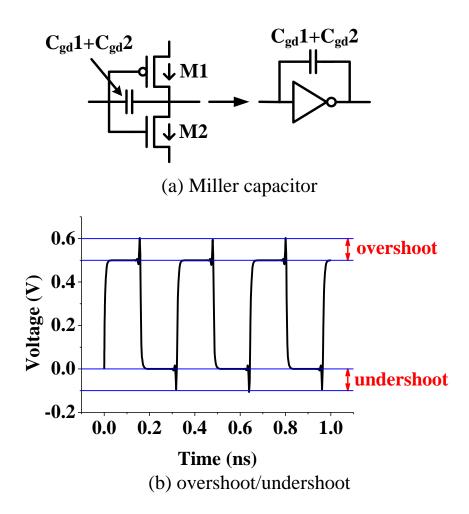

|           | 5.4.3    | Increased Miller Capacitance       | 97  |

| 5.5       | HETT-F   | Based SRAM Design                  | 100 |

|           | 5.5.1    | Limitations in Standard 6-T SRAM   | 100 |

|           | 5.5.2    | HETT-Based 7-T SRAM                | 104 |

| 5.6       | Conclus  | ion                                | 108 |

| VI. Concl | lusion . |                                    | 110 |

| BIBLIOGRA | PHY      |                                    | 112 |

## LIST OF FIGURES

## Figure

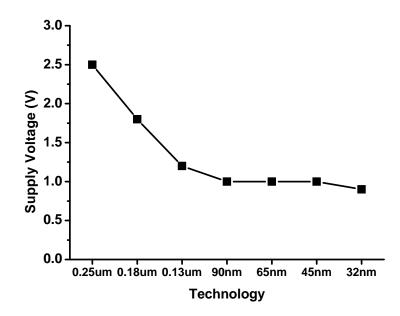

| 1.1  | Technology Scaling Trends of Supply Voltage                       | 3  |

|------|-------------------------------------------------------------------|----|

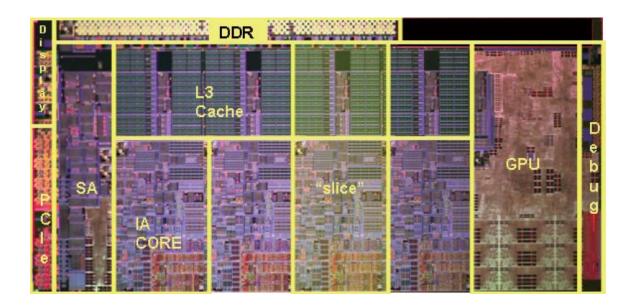

| 1.2  | Die Photo of Intel High Performance 32nm Processor                | 5  |

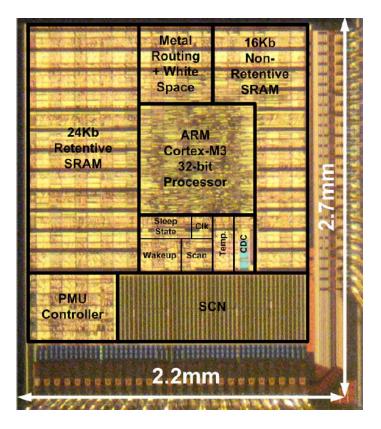

| 1.3  | Die Photo of $0.18\mu$ m Sensor System                            | 5  |

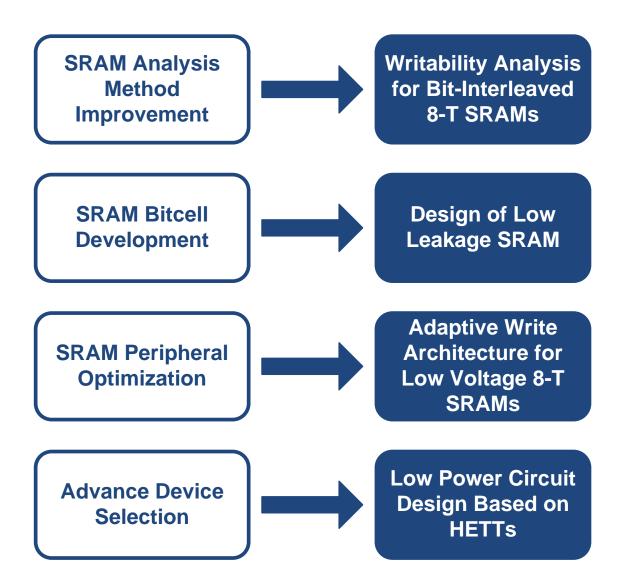

| 1.4  | Approaches for Analysis and Design of Robust Low Voltage SRAM     | 7  |

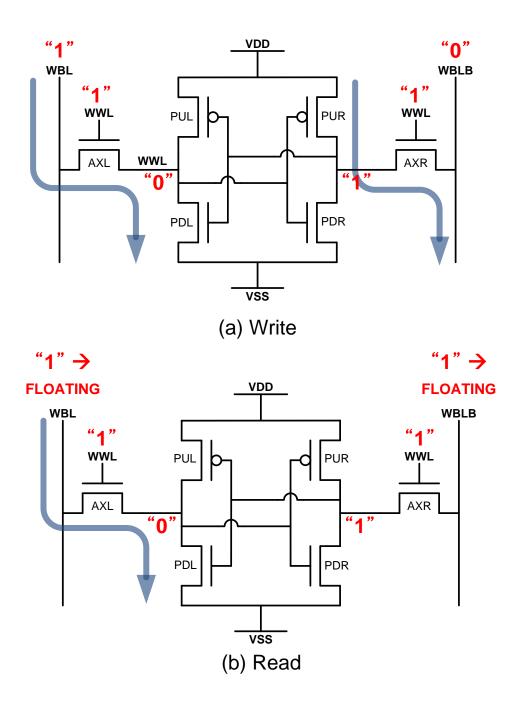

| 2.1  | SRAM Write and Read Operations                                    | 14 |

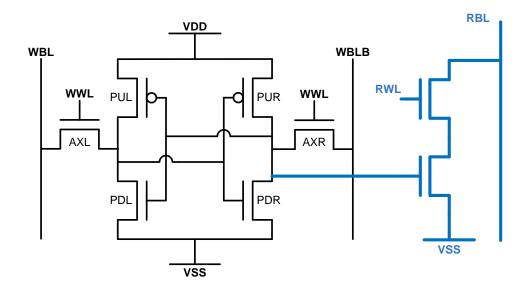

| 2.2  | 8-T SRAM Schematic                                                | 15 |

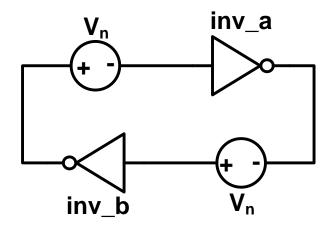

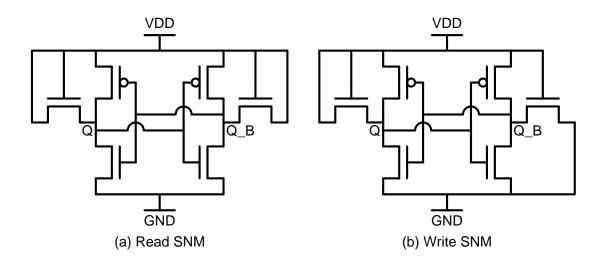

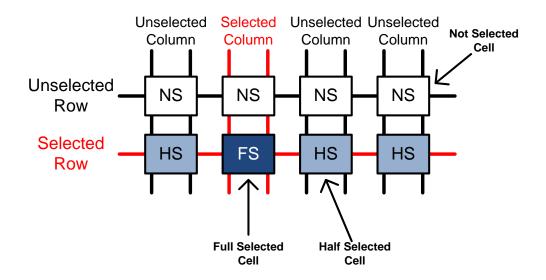

| 2.3  | Static Noise Margin Schematic                                     | 16 |

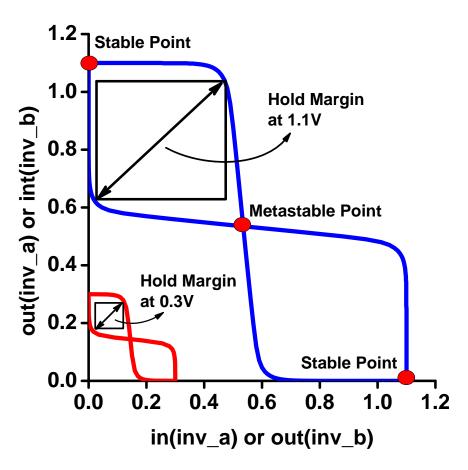

| 2.4  | Butterfly Curves for Hold Margin                                  | 17 |

| 2.5  | Schematics for Measuring Read and Write SNM $\ . \ . \ . \ . \ .$ | 17 |

| 2.6  | Butterfly Curves for Read/Write Margin                            | 18 |

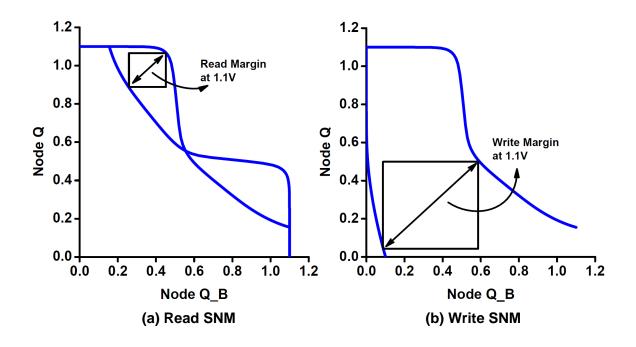

| 2.7  | Three Different Scenarios of Soft Errors                          | 19 |

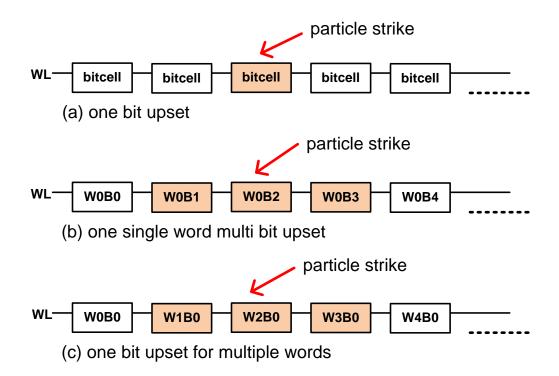

| 2.8  | Half Select Disturb in Bit-Interleaved Array                      | 20 |

| 2.9  | The Definition of $T_{crit}$                                      | 22 |

| 2.10 | Worst Case Corner Directions                                      | 24 |

| 2.11 | Worst Case Corner Simulation Results                              | 25 |

| 2.12 | Bit-interleaved Writability Analysis                              | 27 |

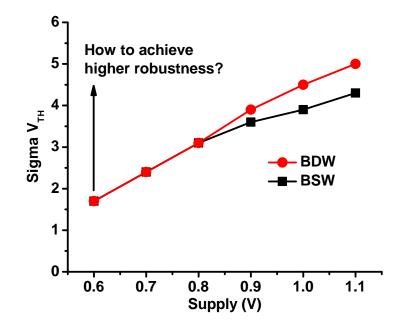

| 2.13 | Bit-interleaved Writability as Voltage Scales                              | 28 |

|------|----------------------------------------------------------------------------|----|

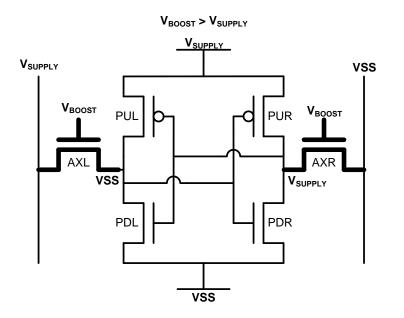

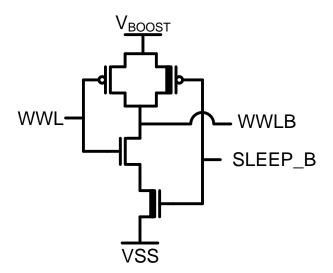

| 2.14 | Word-line Boosting Schematic                                               | 29 |

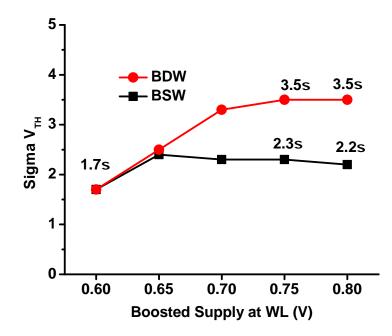

| 2.15 | Bit-interleaved Writability with Word-line Boosting $\ldots \ldots \ldots$ | 29 |

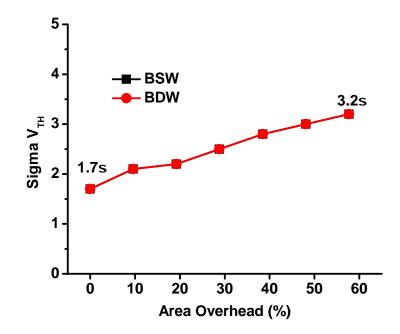

| 2.16 | Bit-interleaved Writability with Device Sizing                             | 30 |

| 2.17 | Bit-interleaved Writability with Both Word-line Boosting and Device Sizing | 31 |

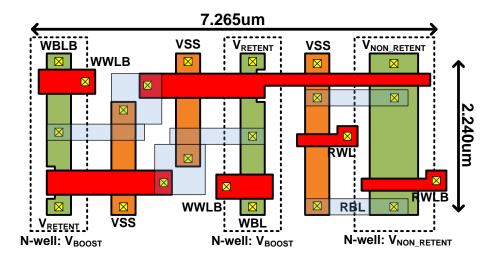

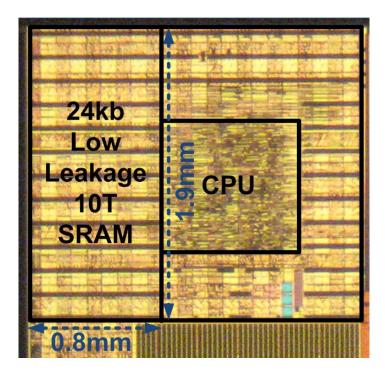

| 3.1  | Low Leakage 10-T SRAM Layout                                               | 35 |

| 3.2  | Leakage Source in MOS devices                                              | 37 |

| 3.3  | Transistor Stacking Schematic                                              | 38 |

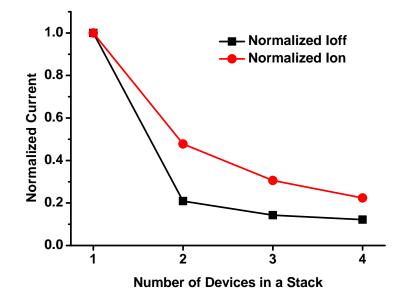

| 3.4  | Leakage Reduction via Transistor Stacking                                  | 39 |

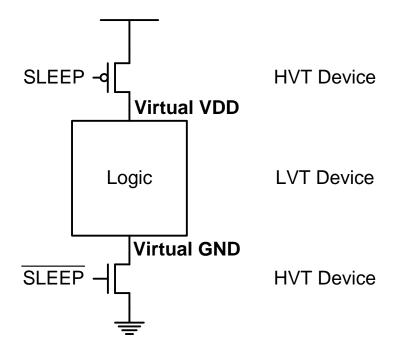

| 3.5  | Power Gating Concept                                                       | 40 |

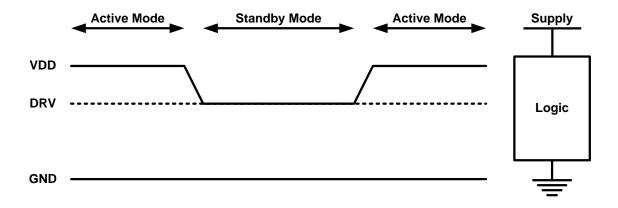

| 3.6  | Supply Voltage Ramping Timing Diagram                                      | 42 |

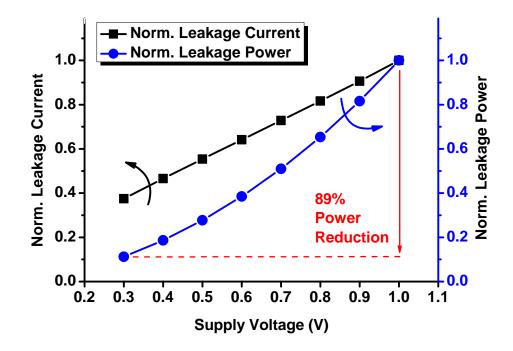

| 3.7  | Leakage Reduction by Supply Voltage Ramping                                | 43 |

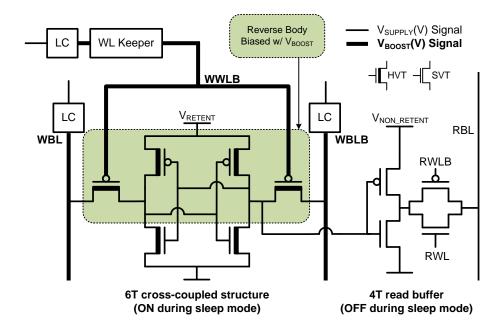

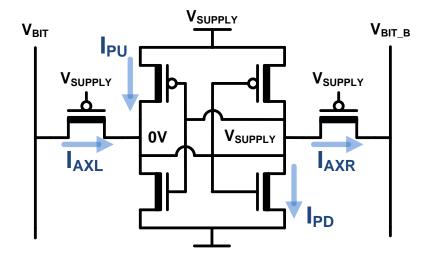

| 3.8  | Low Leakage 10-T SRAM Schematic                                            | 45 |

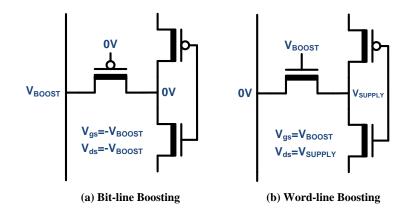

| 3.9  | Comparison Between Bit-line Boosting and Word-line Boosting                | 46 |

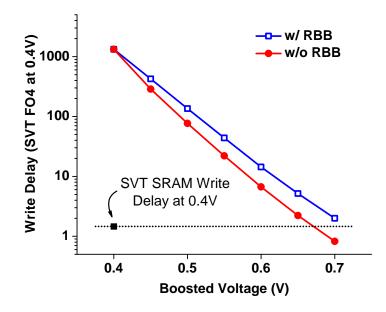

| 3.10 | Bit-line Boosting Simulation Results                                       | 47 |

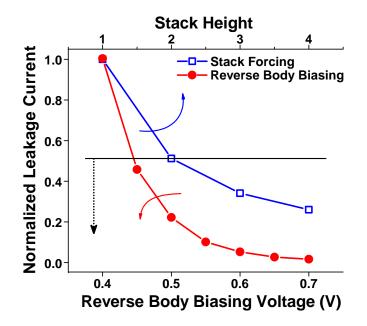

| 3.11 | Comparison of Reverse Body Biasing and Stack Forcing                       | 48 |

| 3.12 | SRAM Leakage Paths during Standby Mode                                     | 49 |

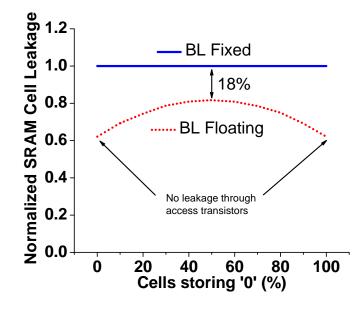

| 3.13 | The Effect of Bit-line Floating on Leakage Reduction                       | 50 |

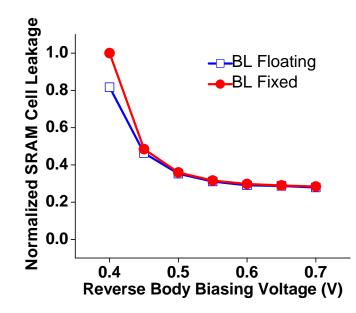

| 3.14 | SRAM Leakage and PMOS Reverse Body Biasing                                 | 50 |

| 3.15 | Design of Word-line Keeper                                                 | 51 |

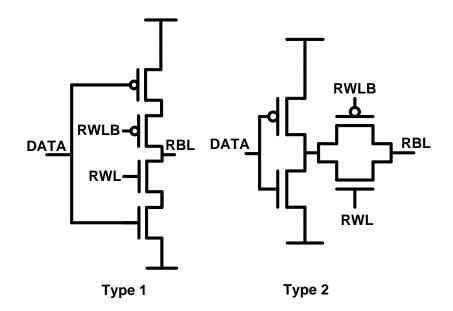

| 3.16 | Two Different 4-T Read Buffers                                             | 52 |

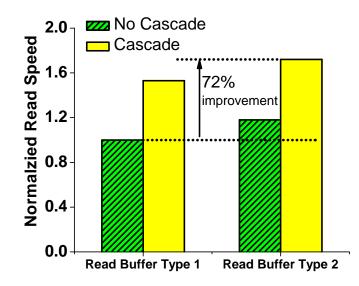

| 3.17 | Read Buffers Performance Comparison                                        | 53 |

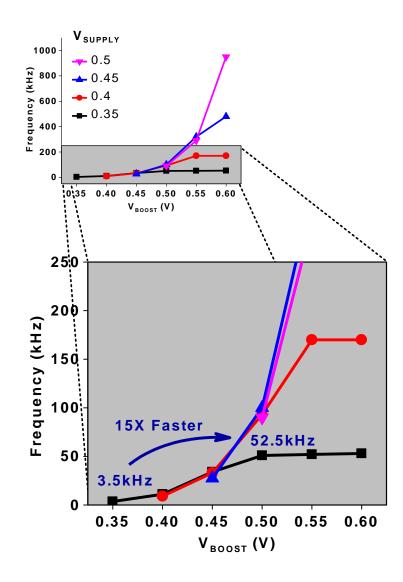

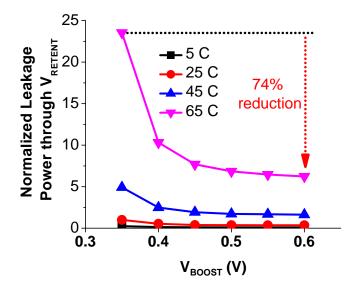

| 3.18 | Measured SRAM Performance Improvement                                            | 54 |

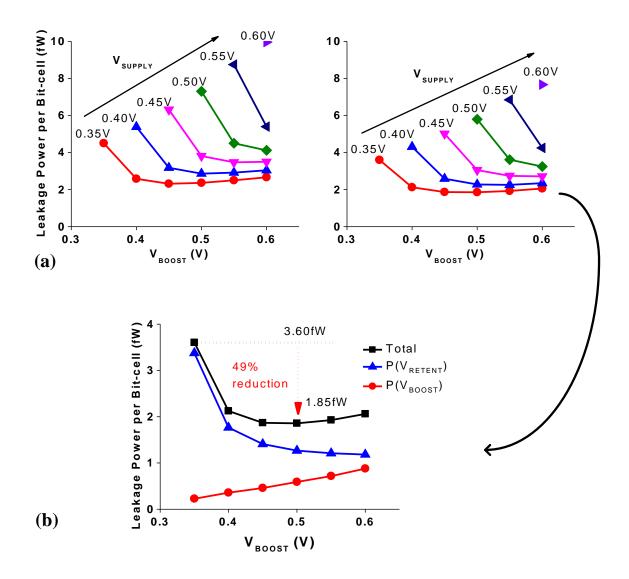

|------|----------------------------------------------------------------------------------|----|

| 3.19 | Measured SRAM Leakage                                                            | 55 |

| 3.20 | Temperature Variation of Measured Leakage                                        | 56 |

| 3.21 | Chip Micrograph and Dimension                                                    | 57 |

| 4.1  | FO4 Delay over Supply                                                            | 61 |

| 4.2  | Read vs. Write at Low Voltage                                                    | 61 |

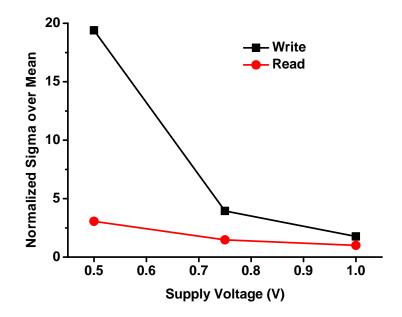

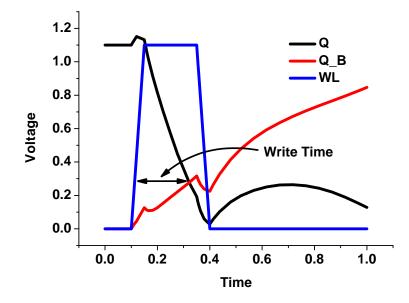

| 4.3  | SRAM Write Time                                                                  | 62 |

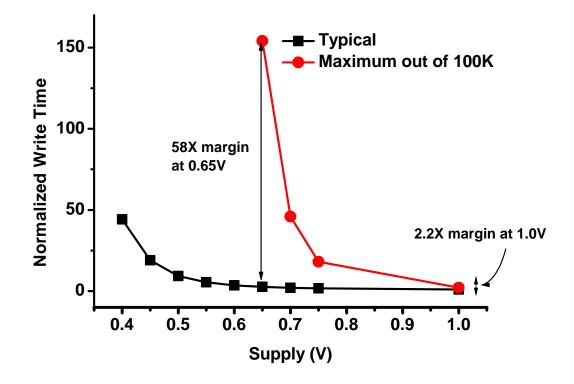

| 4.4  | SRAM Write Time as Supply Scales                                                 | 63 |

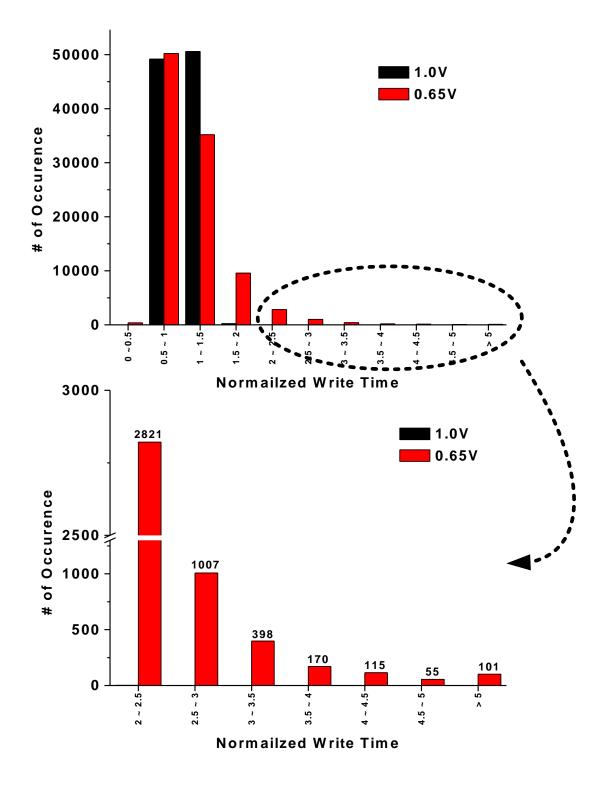

| 4.5  | SRAM Write Time Distribution at 0.65V and 1.0V $\ldots$                          | 65 |

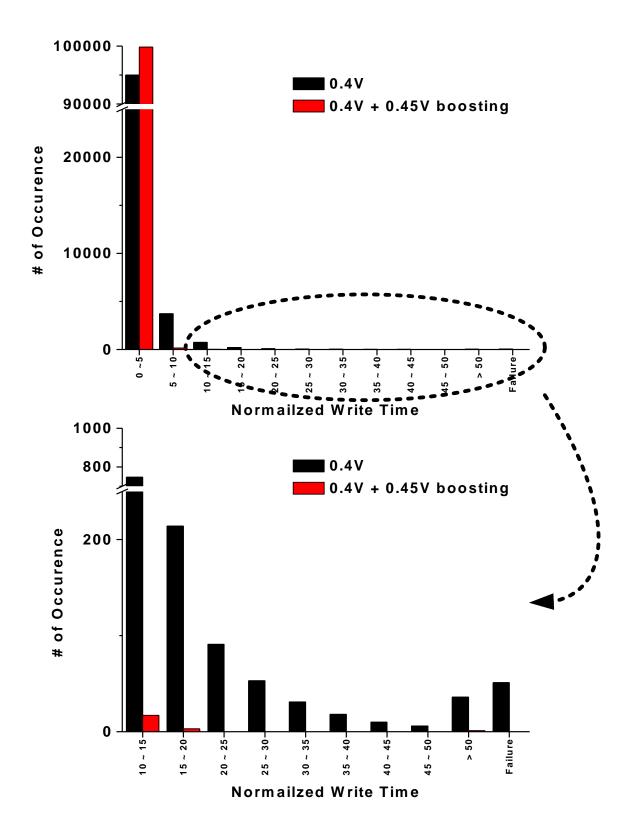

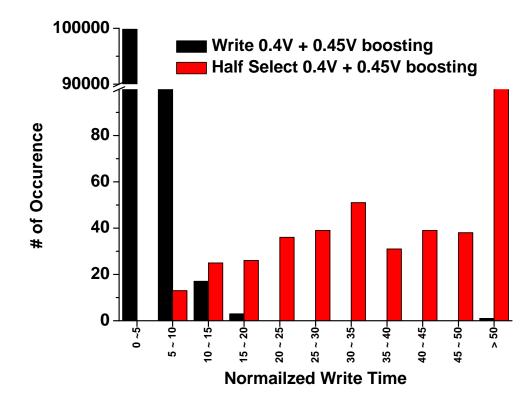

| 4.6  | SRAM Write Time Distribution at $0.4V$ with and without Boosting                 | 67 |

| 4.7  | SRAM Half Select with WWL Boosting                                               | 68 |

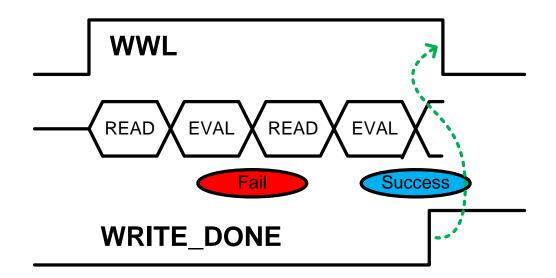

| 4.8  | High Level Timing Diagram of Adaptive Write Architecture                         | 70 |

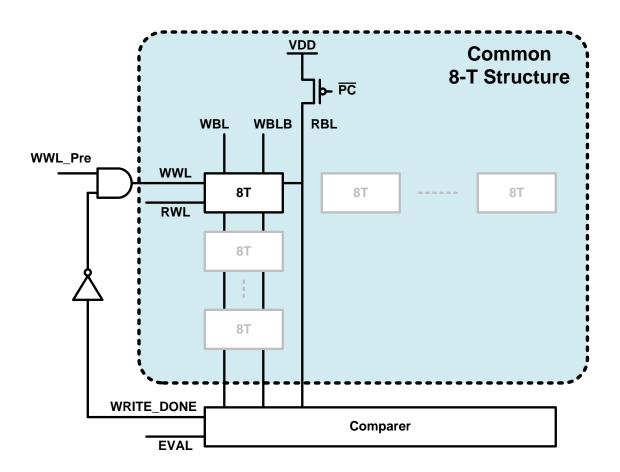

| 4.9  | High Level Block Diagram of Adaptive Write Architecture                          | 71 |

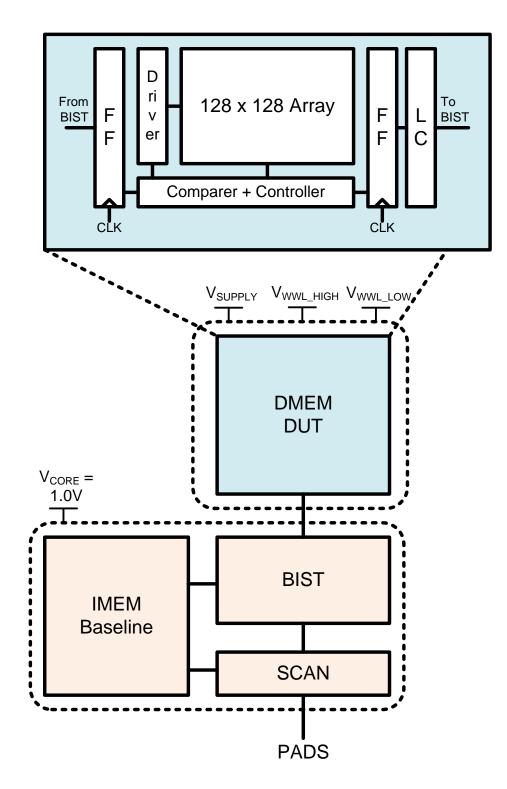

| 4.10 | Block Diagram of Prototype Implemation                                           | 73 |

| 4.11 | A cascaded bit-line Structure                                                    | 75 |

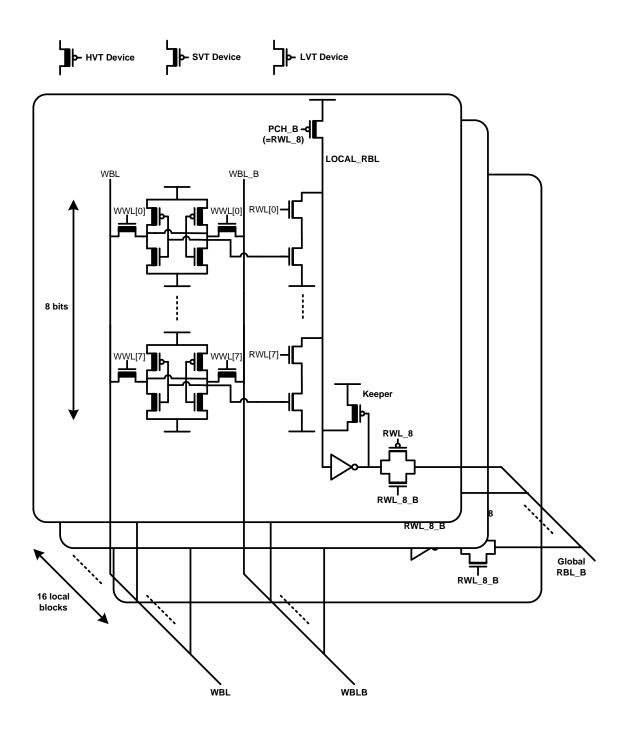

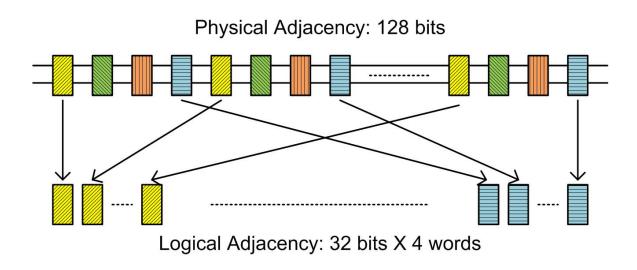

| 4.12 | Bit-Interleaved Bitcells Structure                                               | 76 |

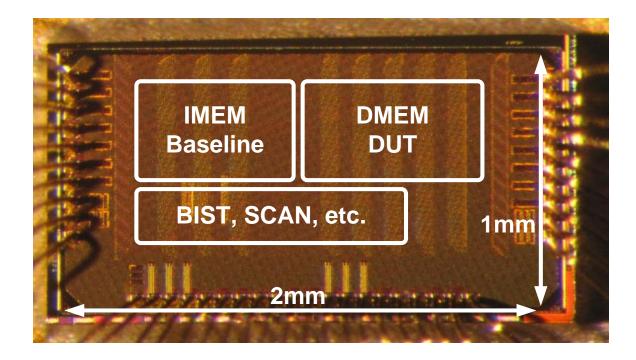

| 4.13 | Chip Micrograph                                                                  | 76 |

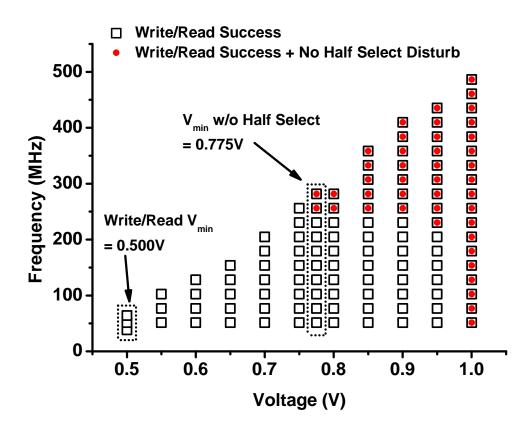

| 4.14 | A Shmoo Plot to Find the $V_{min}$ with Normal Write/Read Operation              | 77 |

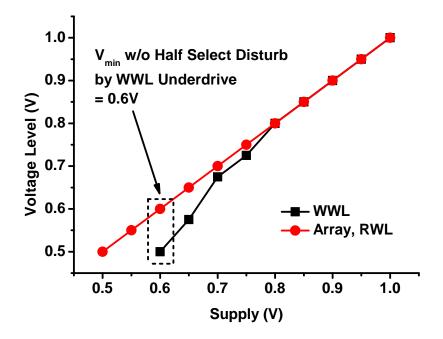

| 4.15 | WWL Underdrive to Fix Half Select Disturb                                        | 77 |

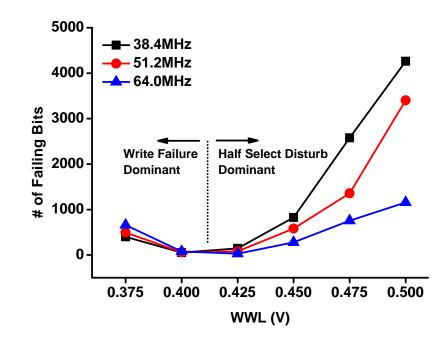

| 4.16 | Failing Bits at 500mV with WWL Underdrive                                        | 78 |

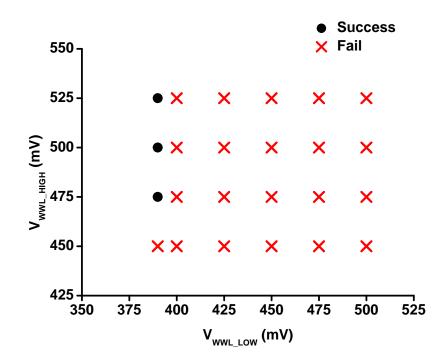

| 4.17 | WWL Shmoo at 0.5V                                                                | 79 |

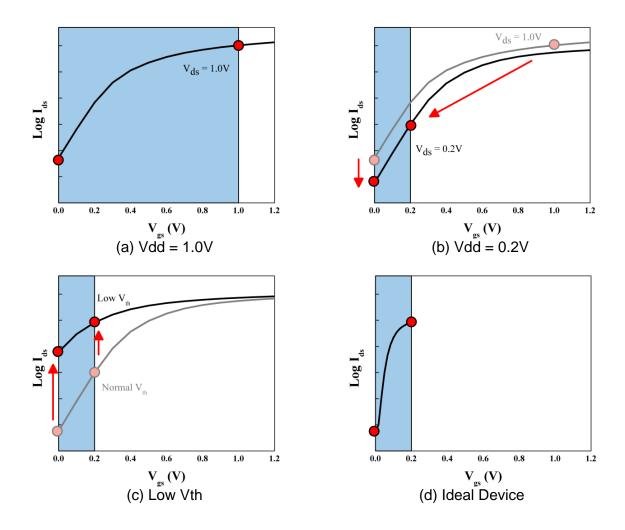

| 5.1  | Motivation on Developing Devices with Steep Subthreshold Swing $% \mathcal{A}$ . | 85 |

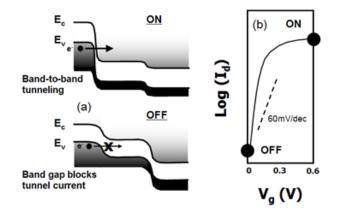

| 5.2  | Tunneling FET Device Concept                                                     | 87 |

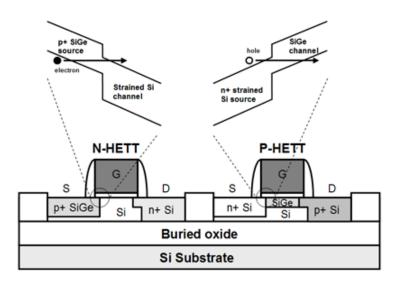

| 5.3  | CMOS-Compatible Implementation of Complementary Tunneling FETs                 | 88  |

|------|--------------------------------------------------------------------------------|-----|

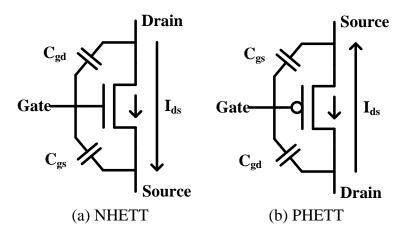

| 5.4  | Device Symbols for HETTs                                                       | 91  |

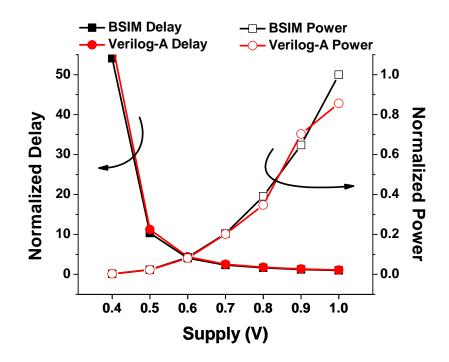

| 5.5  | BSIM vs. Verilog-A                                                             | 91  |

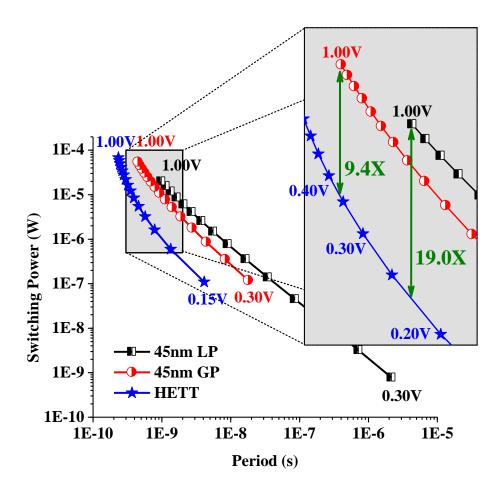

| 5.6  | Comparison of Dynamic Power Consumption                                        | 93  |

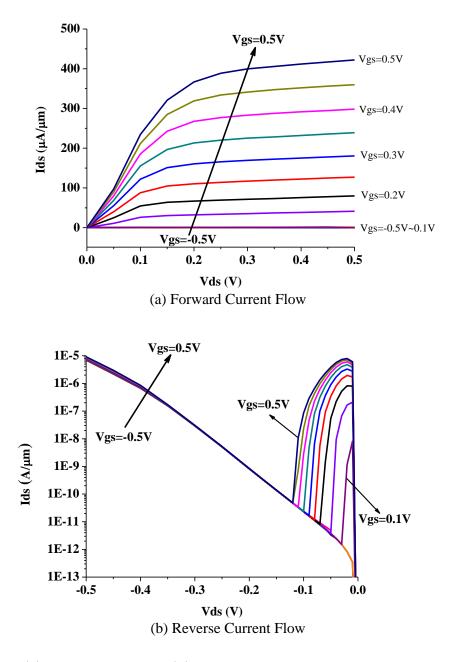

| 5.7  | Forward and Reverse Bias Drain Current of HETT                                 | 95  |

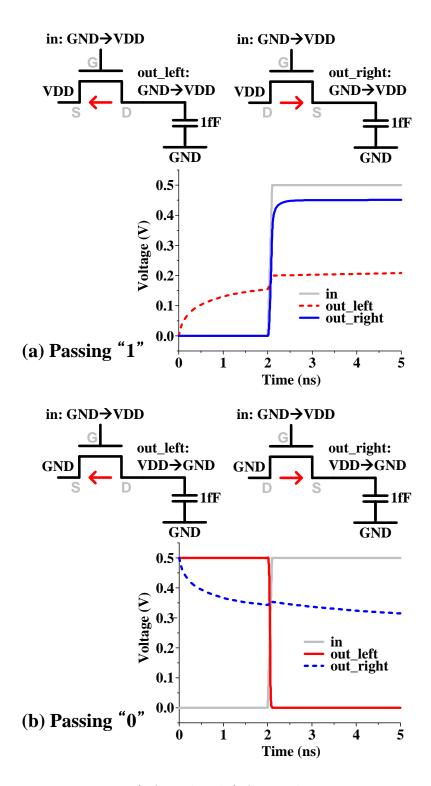

| 5.8  | Limitation of HETT-Based Pass-Gates                                            | 96  |

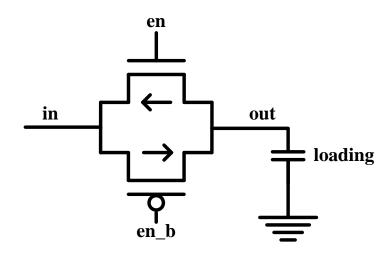

| 5.9  | HETT-Based Transmission-Gate                                                   | 97  |

| 5.10 | Miller Capacitance of HETT                                                     | 98  |

| 5.11 | $C_{gd}$ Comparison                                                            | 99  |

| 5.12 | Overshoot effects in HETT                                                      | 100 |

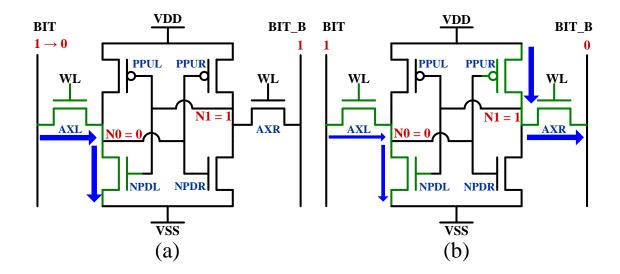

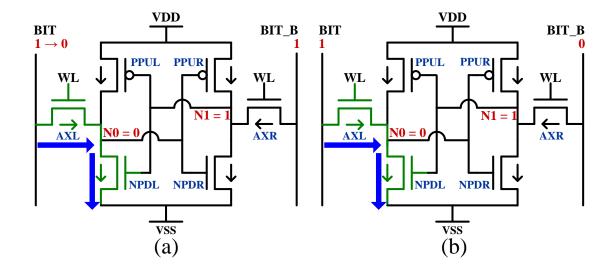

| 5.13 | CMOS 6-T Read and Write Operations                                             | 101 |

| 5.14 | HETT 6-T Read and Write Operations with Inward Direction Access<br>Transistors | 102 |

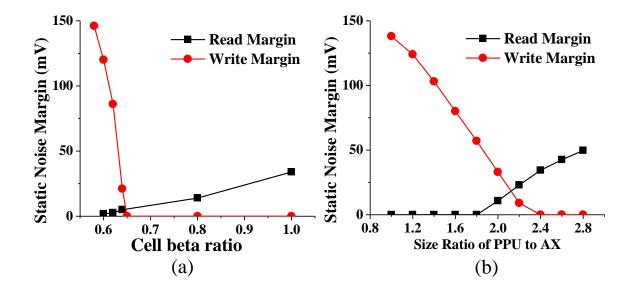

| 5.15 | Static Noise Margins of HETT 6-T SRAM                                          | 103 |

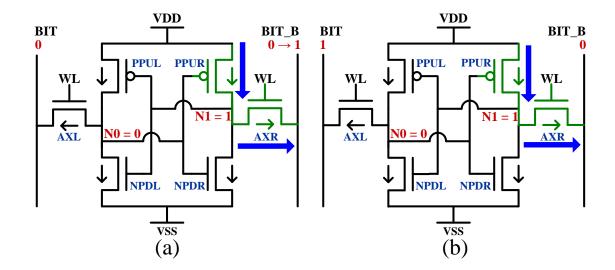

| 5.16 | HETT 6-T Read and Write Operations with Outward Direction Access Transistors   | 104 |

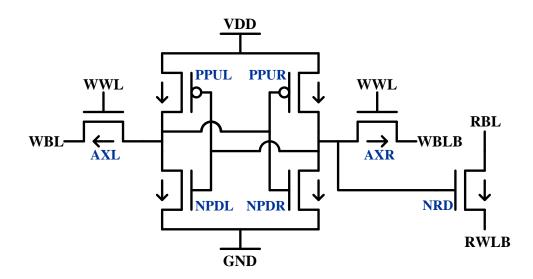

| 5.17 | Proposed HETT 7-T SRAM Structure                                               | 105 |

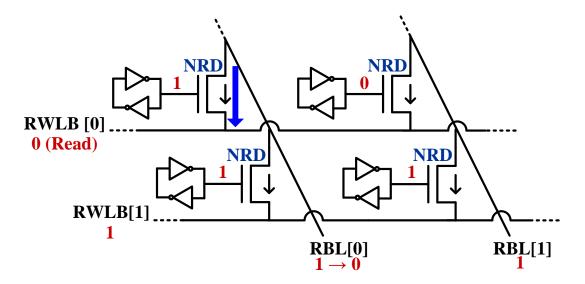

| 5.18 | Read Operation in 7-T SRAM Array                                               | 106 |

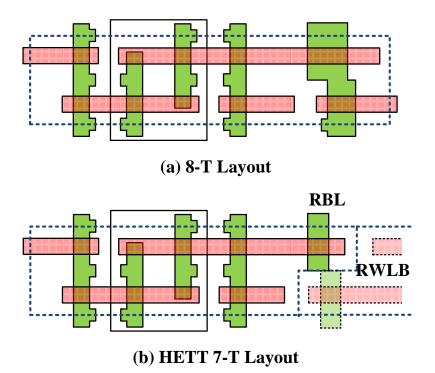

| 5.19 | HETT 7-T Layout                                                                | 107 |

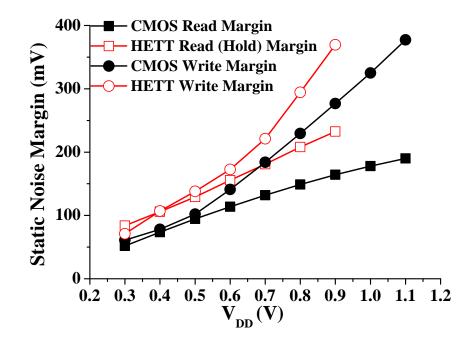

| 5.20 | Read/Write Margin Comparison                                                   | 108 |

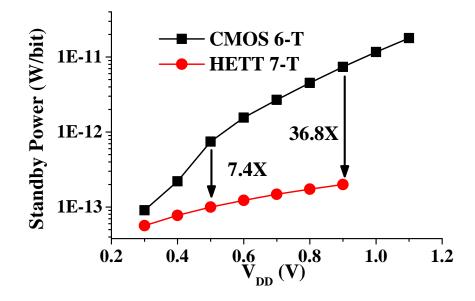

| 5.21 | Standby Power Comparison                                                       | 109 |

# LIST OF TABLES

## <u>Table</u>

| 1.1 | Tradeoffs of SRAM Solutions                                                                 | 6  |

|-----|---------------------------------------------------------------------------------------------|----|

| 3.1 | Sleep Power Breakdown of a Sensor Application                                               | 34 |

| 3.2 | Body Biasing Operation                                                                      | 42 |

| 3.3 | Low Leakage 10-T SRAM Operation Modes                                                       | 45 |

| 3.4 | SRAM Failures According to Speed                                                            | 53 |

| 4.1 | Static Write Failures and Yield below $0.65 V$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 64 |

| 4.2 | Dynamic Write Failures Increases as WWL Pulse Width Decreases at 0.65V                      | 64 |

| 4.3 | Voltage Level Modulation                                                                    | 72 |

| 4.4 | Supplies for Each $V_{min}$ Cases $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 79 |

| 4.5 | Adaptive Write Architecture Power Measurement                                               | 80 |

## LIST OF ABBREVIATIONS

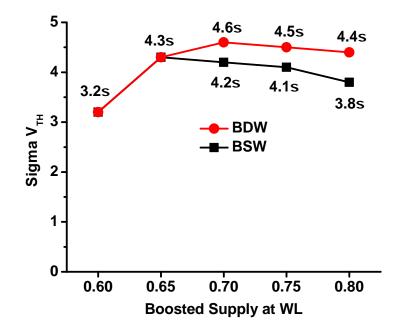

- **BDW** Bit-interleaved Dynamic Writability

- **BSIM** Berkeley Short-channel IGFET Model

- **BIST** Built In Self Test

- **BSW** Bit-interleaved Static Writability

**CMOS** Complementary Metal-Oxide-Semiconductor

- **CPU** Central Processing Unit

- **CSV** Comma-Separated Values

- DC Direct Current

- **DUT** Design Under Test

- **DMEM** Data Memory

- **DW** Dynamic Writability

- FO4 Fan-Out of 4

- **HETT** Heterojunction Tunneling Transistor

- **HVT** High Threshold Voltage

- **IMEM** Instruction Memory

- LER Line Edge Roughness

- LDO Low-Dropout Regulator

- **LVT** Low Threshold Voltage

- MOS Metal-Oxide-Semiconductor

- **MOSFET** Metal-Oxide-Semiconductor Field-Effect Transistor

MTCMOS Multithreshold-Voltage CMOS

**NAND** Negated AND

$\mathbf{NHETT}$  N-channel HETT

${\bf NMOS}\,$  N-channel MOS

NTC Near-Threshold Computing

**PC** Personal Computer

**PDN** Pull-Down Network

${\bf PMOS}\,$  P-channel MOS

**PHETT** P-channel HETT

**PUN** Pull-Up Network

**PVT** Process, Voltage, and Temperature

SCN Switched-Capacitor Networks

**SECDED** Single Error Correction/Double Error Detection

${\bf SNM}\,$  Static Noise Margin

SoC System on Chip

**SRAM** Static Random Access Memory

**SW** Static Writability

${\bf SVT}\,$  Standard Threshold Voltage

**RBL** Read Bit-Line

**RDF** Random Dopant Fluctuation

RO Ring Oscillator

**T-CAD** Technology Computer Aided Design

**VLSI** Very-Large-Scale Integration

**WBL** Write Bit-Line

**WBLB** Write Bit-Line Bar

WL Word-Line

**WWL** Write Word-Line

#### ABSTRACT

Design and Analysis of Robust Low Voltage Static Random Access Memories

by

Daeyeon Kim

Chair: Dennis Michael Sylvester

Static Random Access Memory (SRAM) is an indispensable part of most modern VLSI designs and dominates silicon area in many applications. In scaled technologies, maintaining high SRAM yield becomes more challenging since they are particularly vulnerable to process variations due to 1) the minimum sized devices used in SRAM bitcells and 2) the large array sizes. At the same time, low power design is a key focus throughout the semiconductor industry. Since low voltage operation is one of the most effective ways to reduce power consumption due to its quadratic relationship to energy savings, lowering the minimum operating voltage ( $V_{min}$ ) of SRAM has gained significant interest.

This thesis presents four different approaches to design and analyze robust low voltage SRAM: SRAM analysis method improvement, SRAM bitcell development, SRAM peripheral optimization, and advance device selection.

We first describe a novel yield estimation method for bit-interleaved voltage-scaled 8-T SRAMs. Instead of the traditional trade-off between write and read, the trade-off between write and half select disturb is analyzed. In addition, this analysis proposes a method to find an appropriate Write Word-Line (WWL) pulse width to maximize yield.

Second, low leakage 10-T SRAM with speed compensation scheme is proposed. During sleep mode of a sensor application, SRAM retaining data cannot be shut down so it is important to minimize leakage in SRAM. This work adopts several leakage reduction techniques while compensating performance.

Third, adaptive write architecture for low voltage 8-T SRAMs is proposed. By adaptively modulating WWL width and voltage level, it is possible to achieve low power consumption while maintaining high yield without excessive performance degradation.

Finally, low power circuit design based on heterojunction tunneling transistors (HETTs) is discussed. HETTs have a steep subthreshold swing beneficial for low voltage operation. Device modeling and design of logic and SRAM are proposed.

## CHAPTER I

## Introduction

There has been an ever growing necessity for battery-operated systems. Batteryoperated systems include handheld devices as well as sensor applications. Many people have used cell phones and a significant portion of cell phones are now high performance smart phones. In addition to cell phones, battery-operated tablet Personal Computer (PC)s start encroaching into the territory of traditional desktop and laptop PCs. It is highly expected that the market of smart phones and tablet PCs will grow even more. A necessity for sensor applications also has increased. Health-monitoring sensors implanted in a human body and infrastructure monitoring sensor networks are good examples of sensor applications with high demand. To develop more powerful and smaller battery-operated systems, technology scaling and low power design has been two main driving forces.

Technology scaling has acted an important role in the design of high performance System on Chip (SoC) for the past several decades by integrating more devices in a smaller area. First of all, technology scaling makes it possible to build a high performance Central Processing Unit (CPU) which runs at several GHz. Next, it also makes it possible to build a smaller system which has the same or even higher performance than before. For example, an intraocular sensor implanted in a human eye for curing glaucoma [13] needs a small form-factor and technology scaling enables Low power design is indispensible to realize battery-operated systems. It is impossible to use a large battery in a handheld device or a sensor application due to limited sizes of them and a short battery lifetime of a small battery limits the usage of them. Even more, by technology scaling, more devices are integrated in a system and therefore a chip consumes more power. Low power design can extend a battery lifetime by optimizing power consumption of a device.

Analysis and design of robust low voltage SRAM is one of the essential parts for technology scaling and low power design to realize a smaller battery-operated SoC with a long lifetime. In modern SoC, a significant amount of area is used for SRAM and more aggressive scaling is applied to SRAM for denser integration. Hence, maintaining a high yield of SRAM and reducing power consumption of SRAM are necessary. Also, a battery-operated system spends a large portion of its lifetime in standby mode so it is very important to reduce the leakage power of SRAM which cannot be shutdown in standby mode. The most common way for power reduction is the low voltage operation. However, the low voltage operation compromises robustness and performance. Therefore, low voltage SRAM optimized for a given target application is essential to realize more advanced battery-operated systems.

#### 1.1 Technology Scaling and Low Power Design

Over the past several decades, the number of transistors in a chip has increased exponentially (Moore's Law [47]). By decreasing the minimum feature size in integrated circuits, more devices are integrated in a small area, performance increases, and power consumption decreases.

However, even though the minimum feature size has decreased, the benefits of technology scaling have diminished today. One of the largest barriers of technology scaling is related to power consumption. The supply voltage has remained almost

it.

Figure 1.1: Technology scaling trends of supply voltage

constant [19] but leakage current has increased exponentially [48]. Figure 1.1 depicts supply voltage trends with technology scaling. Supply voltage has been stagnant at near 1V after 90nm technology but the total number of transistors in a chip has continuously grown. As a result, it is becoming more difficult to make an energy efficient system.

Variability is another barrier for scaling technology [3]. Random Dopant Fluctuation (RDF) [45] and Line Edge Roughness (LER) [23] induce a significant  $V_{th}$ variation and performance variation.

As discussed above, optimizing power consumption is one of the most important issues in advanced technology nodes. Low power design techniques are important over the entire range Near-Threshold Computing (NTC): high performance platforms, personal computing platforms, and sensor-based platforms. If a system is designed for high performance, active power reduction is the most important. However, leakage power reduction techniques are more crucial in sensor-based platforms because an activity ratio in a sensor-based system is extremely low. In cases of personal computing platforms, balancing leakage power reduction techniques and active power reduction techniques is necessary. If voltage scaling is adopted for power reduction, it is also important to mitigate a larger variation at low voltage. Therefore, low power design includes active power reduction techniques, leakage power reduction techniques, and variation mitigating techniques at low voltage.

NTC is one of recently proposed architecture to minimize power consumption and mitigate performance degradation using highly parallelized voltage scaled processors [19]. Finding an optimal trade-off point between power reduction and performance degradation by voltage scaling is the underlying idea of NTC.

### 1.2 Challenges of Designing Low Voltage SRAM

From high performance platforms to sensor-based platforms, the importance of designing robust low power SRAM must be emphasized for several reasons: dominance in area, critical yield issue, and large array sizes.

A significant amount of area is used for SRAM in modern SoC. Figure 1.2 shows the most recent high performance CPU from Intel. Excluding the area of a graphic core and a memory controller integrated in this processor, the L3 cache shown in the die photo and lower level caches integrated in cores spend about 50% of total area. In a case of sensor-based application, the dominance in area of SRAM does not alter. A sensor application developed by University of Michigan also spends about 50% of its area for SRAM (Figure 1.3). Because of the large area dedicated to SRAM, a portion of power consumption by SRAM is significant in modern SoC too.

Maintaining high SRAM yield becomes more challenging because they are particularly vulnerable to process variation. This is because minimum or smaller than minimum sized devices are used in SRAM and the size of array are very large (up to 10s of MB). Voltage scaling for power reduction aggravates robust SRAM operations. Process variation increases as voltage scales and it makes already limited SRAM

Figure 1.2: Die Photo of Intel High Performance 32nm Processor [71]

Figure 1.3: Die Photo of University of Michigan  $0.18\mu$ m Sensor System [11]

| Solution        | Power          | Performance | Area          | Yield(Robustness) |

|-----------------|----------------|-------------|---------------|-------------------|

| Device Sizing   | Worse          | Better      | Worse         | Better            |

| Voltage Scaling | Better         | Worse       | Same or Worse | Worse             |

| 8-T SRAM        | Vary by Design | Better      | Worse         | Better            |

| Assist Circuits | Vary by Design | Better      | Worse         | Better            |

Table 1.1: There are different trade-offs in each solution.

yield worse. Also, low supply voltage impacts the reliability of SRAM [5]. Gate oxide degradation and soft error susceptibility are two important reliability challenges in voltage scaled SRAM design.

Many techniques have been proposed to solve prevailing issues in low voltage SRAM design. In Table 1.1, the traditional solutions for robust low voltage SRAM design are shown and the trade-offs in each solution are compared. The size of devices in SRAM can increase for increased yield and higher performance and but it will result in increased total area and higher power consumption. Voltage scaling can be adopted for power saving but performance will be degraded and yield will be compromised. Using different SRAM bitcells is another approach. With 8-T SRAM bitcell, performance and yield will be improved but the larger area of 8-T SRAM bitcell cannot be avoided. To support a particular SRAM operation, write or read assist circuit can be used. However, there is a chance to spend extra area for the assist circuits. As shown above, there are trade-offs in each solution. Therefore, it is important to choose appropriate techniques and optimize them for a target application.

#### **1.3** Contributions of This Work

A main purpose of this work is to analyze and design of low voltage SRAM with high yield and low power consumption. To achieve this goal, there are different approaches (Figure 1.4).

Figure 1.4: Approaches for analysis and design of robust low voltage SRAM

The first approach is SRAM analysis method improvement. During design phase or even testing phase, appropriate analyzing methods to measure SRAM yield are necessary for correct and fast yield estimation. Static Noise Margin (SNM) method has acted an important role for robustness estimation of SRAM bitcell for more than 20 years [61]. However, as new SRAM bitcells are developed and complicated yield related issues appear, a dedicated analysis method for a given case is necessary for more accurate and faster estimation of SRAM robustness. In Chapter II [33], a writability analysis method for bit-interleaved voltage-scaled 8-T SRAMs is proposed to maximize writability while minimizing half select disturb. For robust SRAM operations at low voltage, 8-T SRAM bitcell is used. However, it suffers from half select disturb if bitcells are interleaved. This analysis proposes a method to find an appropriate WWL pulse width to maximize yield.

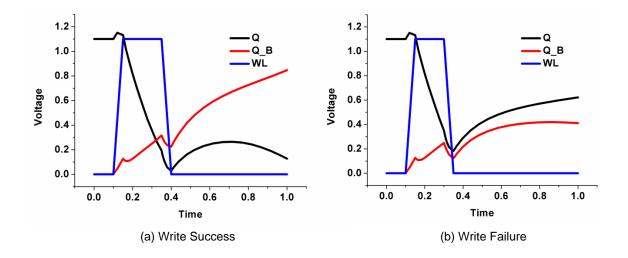

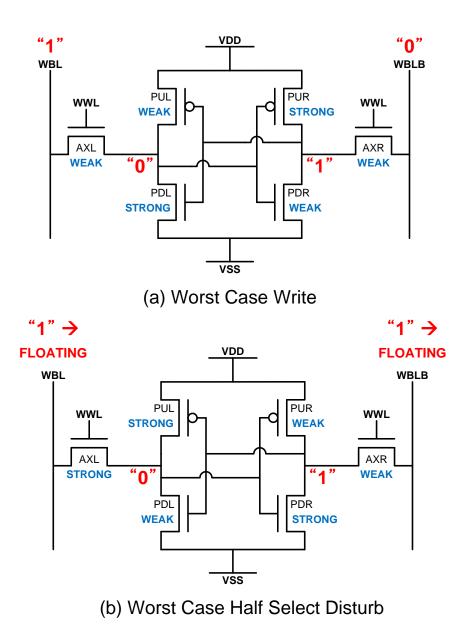

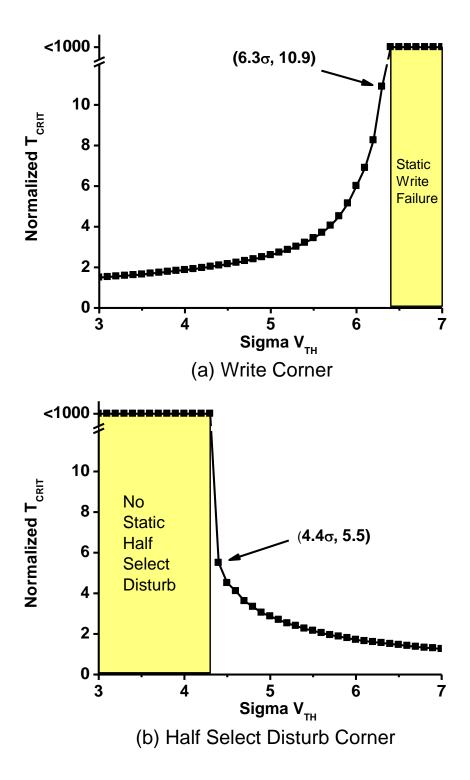

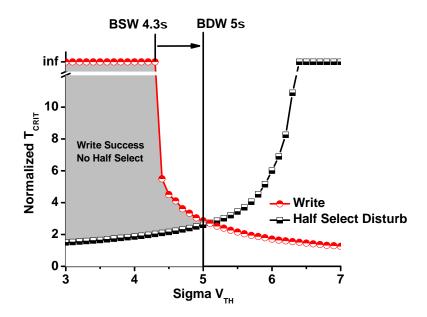

SRAM bitcell development other than 6-T SRAM bitcell is another approach to develop robust low voltage SRAM. A 6-T SRAM bitcell has been a main component of SRAM arrays for the past several decades. However, as technology and voltage scales, it is hard to maintain enough margins for read and write operations with the 6-T SRAM bitcell. To overcome this limitation, an 8-T SRAM bitcell has been introduced [8, 9]. In addition to the 8-T bitcell, other bitcell designs have been proposed for different purposes. A low leakage SRAM with speed compensation scheme is proposed in Chapter III [32]. In this work, a novel 14-T SRAM bitcell is proposed for leakage reduction at the expenses of speed and area. Several leakage reduction techniques are applied to a SRAM array and speed compensation scheme is adopted.